應廣科技PFC460工業級單片機特點

系統特性

高抗干擾(High EFT)系列

特別適用于 AC 電源供電的、阻容降壓電路的、需要較強抗干擾能力的,

或有高 EFT 安規測試要求(±4KV)的產品。

工作溫度范圍:-40°C ~ 85°C

ESD > 8 KV

系統功能

4KW MTP 程序空間供四個 FPPA 單元使用(可編程 1000 次)

512 Bytes SRAM 數據空間供四個 FPPA 單元使用

一個硬件 16 位定時器

兩個 8 位硬件 PWM 生成器 Timer2/Timer3,Timer2/Timer3 還配置 NILRC 振蕩器,它的頻率比 ILRC 更慢,適

合做更省電的喚醒時鐘

Timer2/Timer3 PWM 分辨率可以是 6/7/8bit

三個 11 位硬件 PWM 生成器 PWMG0/PWMG1/PWMG2

一組可設三路 11 位 SuLED(Super LED)PWM 生成器和計數器 LPWMG0/LPWMG1/LPWMG2

提供一個 PFG 硬件電路支持精準的調頻輸出

提供一個硬件比較器

提供一個運算放大器(OPA)

提供 1T 8×8 硬件乘法器

26 個 IO 引腳,都具有可選的上拉/下拉電阻

每個 IO 引腳都具有系統喚醒功能

對于每個設定喚醒功能的 IO,有兩種可選擇的喚醒速度:正常喚醒和快速喚醒

最大 24 IO 引腳可選擇為觸摸按鍵

內置 LDO 硬件電路為觸摸功能提供 2V 電壓基準

內部 Bandgap 電路提供 1.2V 參考電壓

最大 28 通道(包含 GND)12 位 ADC,其中一個通道來自于內部 bandgap 參考電壓或 0.25*VDD

提供 ADC 參考高電壓選項:外部輸入,內部 VDD,Bandgap(1.2V),4V,3V,2V

時鐘模式:內部高頻振蕩器(IHRC)、內部低頻振蕩器(ILRC)、外部晶體震蕩器(EOSC)

提供四組 IO 驅動能力以滿足不同的應用需求

(1) PB0 驅動電流可選 0/10mA,灌電流可選 108/20mA

(2) PB2~PB7 驅動電流可選 28/10mA,灌電流可選 75/20mA

(3) PA0~PA4 驅動電流/灌電流= 10mA/ 20mA

(4) PA5~PA7,PB1,PC0~PC7,PD0~PD1 驅動電流/灌電流= 10mA/ 14mA

內建 VDD/2 偏置電壓產生器,可支持 5COM ×21SEG 點陣的 LCD 屏

14 段 LVR 復位設定,從 2.0V 到 4.5V

8 個可選外部中斷輸入腳

CPU 特點

工作模式:四個 FPPATM 處理單元運作模式或單一處理單元運作模式

104 條高效的指令

絕大部分指令都是單周期(1T)指令

可程序設定的堆棧指針和堆棧深度

數據存取支持直接和間接尋址模式,用數據存儲器即可當作間接尋址模式的數據指針(index pointer)

寄存器地址空間、SRAM 數據存儲空間、MTP 程序空間三者互相獨立

訂購/封裝信息

PFC460-S08: SOP8 (150mil);

PFC460-S14: SOP14 (150mil);

PFC460-S16: SOP16 (150mil);

PFC460-S20: SOP20 (300mil);

PFC460-H20: HTSOP20 (150mil);

PFC460-T20: TSSOP20 (173mil);

PFC460-S24: SOP24 (300mil);

PFC460-S28: SOP28 (300mil);

PFC460-T28: TSSOP28 (173mil).

? 封裝尺寸信息請參考官網文件:”封裝信息

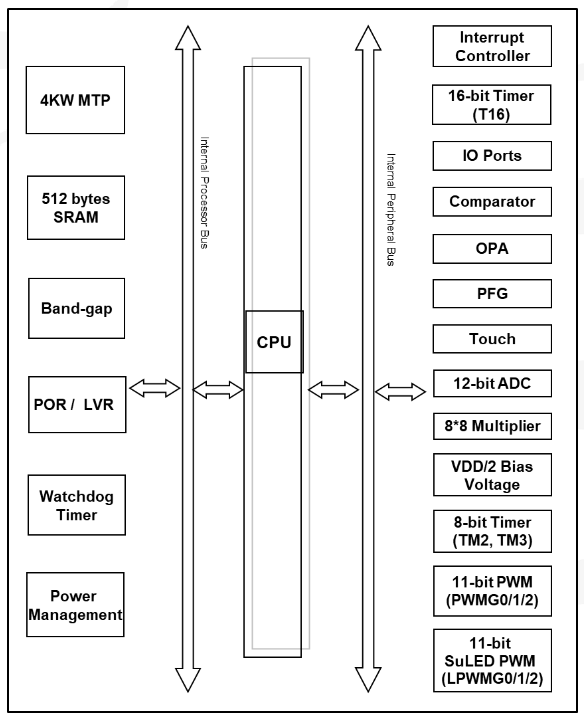

系統概述和方框圖

PFC460 是一個帶 Touch、帶 ADC、并行處理、完全靜態,以 MTP 為程序存儲基礎的處理器,此處理器具

有四個處理單元。它基于 RISC 架構基礎,獲得 (Field Programmable Processor Array 現場可編程處理器陣列)

技術專利。大部分指令的執行周期都是一個指令周期,只有少部分間接尋址的指令需要兩個指令周期。

PFC460 內置 4KW MTP 程序存儲器以及 512 字節 SRAM 數據存儲器。

PFC460 內置 28 通道(包含 GND)12 位分辨率 A/D 轉換器,其中一通道為內部 Bandgap 參考電壓或

0.25*VDD。

PFC460 內置 C-Touch 硬件電路,最大可提供 24 IO 作為觸摸按鍵。

PFC460 提供一個 16 位的硬件計數器(Timer16)、兩個 8 位計數器(Timer2、Timer3)、3 個 11 位計數器

(PWMG0/1/2)和一組新的三路 11 位計數器帶 SuLED PWM 生成器(LPWMG0/1/2)。

PFC460 還提供一個 PFG 調頻電路、運算放大器(OPA)、硬件比較器、驅動 LCD 的 VDD/2 偏置電壓生成

器以及加強硬件運算功能的 8×8 乘法器。

程序結構

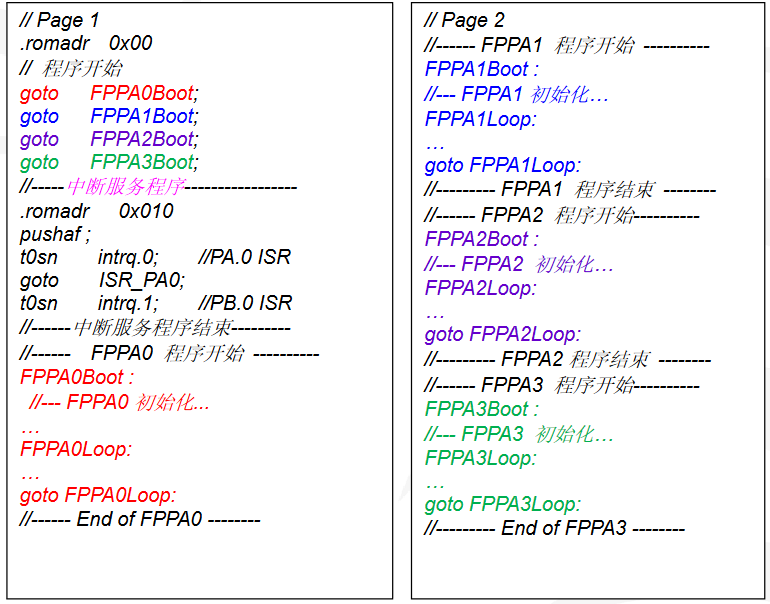

四個處理單元工作模式下程序結構

開機后,FPPA0 ~ FPPA3 的程序開始地址分別是 0x000、0x001、0x002、0x003。中斷服務程序的入口

地址是 0x010,而且只有 FPPA0 才能接受中斷服務。 PFC460 的基本軟件結構如圖 5 所示。四個 FPPA 的處

理單元的程序代碼是被放置在同一個程序空間。除了初始地址和中斷入口地址外,處理單元的程序代碼可以放

在程序存儲器任何位置,并沒有在特定的地址。開機后,將首先執行 FPPA0Boot,其中將包括系統初始化和啟

用其它 FPPA 的單元

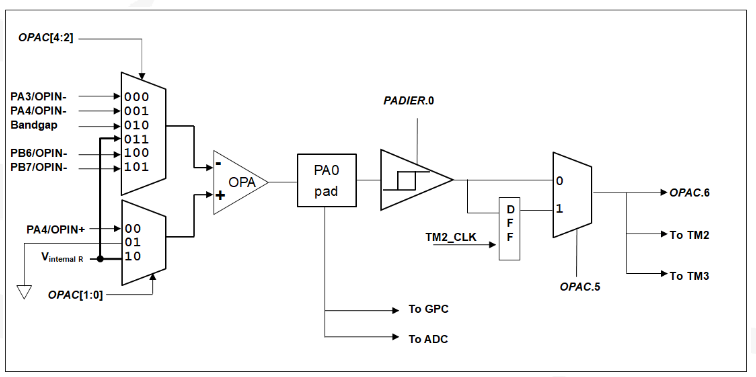

運算放大器(OPA)模塊

PFC460 內置一個運算放大器(OPA)模塊,其基本配置如下圖所示。運算放大器有兩種不同的結構,一

種是 OPA 比較器模式,另一種是 OPA 放大器模式。

OPA 硬件圖框

當用戶通過啟用 OPAC.7 打開 OPA 時,IO 端口 PA0 將成為 OPA 的輸出。用戶可以在放大器模式下通

過 GPC 或 ADC 測量模擬 PA0 電壓,也可以在比較器模式下直接讀取 PA0 的數字 OPA 比較結果

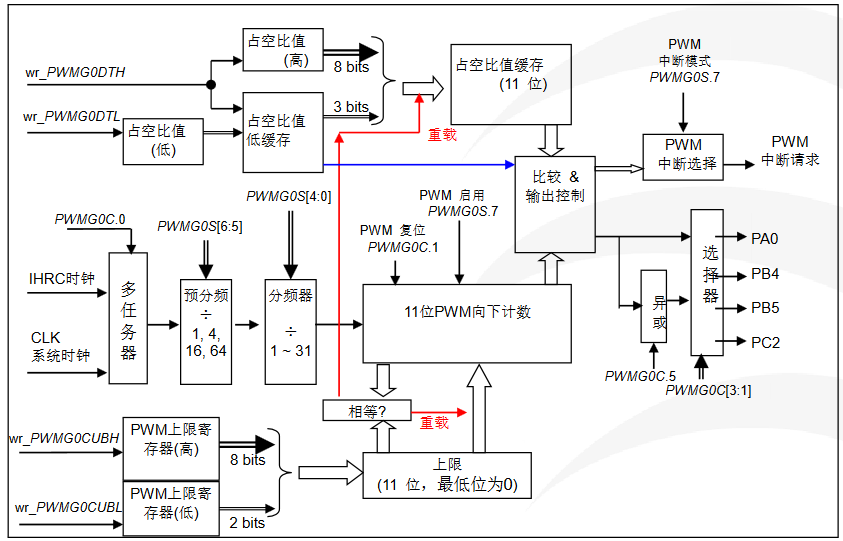

硬件和時鐘框圖

11位PWM 生成器(PWMG0)硬件框圖

燒錄方法

PFC460 的燒錄腳為 VDD, PA3, PA5, PA6, GND。

請使用 PDK5S-P-003 進行燒錄。PDK3S-P-002 或之前的燒錄器皆不支持燒錄 PFC460。

Jumper 連接:可依照燒錄器軟件上的說明,連接 jumper 即可。

13.1. 普通燒錄模式

適用范圍:

單獨封裝 IC,并在燒錄器的 IC 插座或連接分選機燒錄。

合封(MCP)IC,但與 PFC460 合封的 IC 及元件不會被以下電壓破壞,也不會鉗制以下電壓的產生。

普通燒錄模式電壓條件:

(1) VDD 等于 7.5V,而最大供給電流最高可達約 20mA。

(2) PA5 等于 5.8V。

(3) 其他燒錄引腳(GND 除外)等于 VDD。

重要提示:

如在 handler 上對 IC 進行燒錄,請務必按照 APN004 及 APN011 的指示進行。

為對抗燒錄時的雜訊干擾,請于燒錄時在分選機連接 IC 連接器一端的 VDD 和 GND 之間連接 0.01uF 電容。

但切忌連接標值 0.01uF 以上的電容,以免影響普通燒錄模式的運行。

13.2. 在板燒錄模式(On-Board Writing)

PFC460 可以支持在板燒錄。所謂在板燒錄,是指 IC 及其他周邊電路及組件,皆已經焊接到 PCB 上,并對

IC 進行燒錄的情況。在板燒錄需要使用 PDK5S-P-003 上五根引線:ICPCK(PA3)、ICPDA(PA6)、VDD、GND

和 ICVPP(PA5),用于與 IC 上的 PA3、PA6、VDD、GND 和 PA5 對應相連。

若要啟動在板燒錄,請于燒錄器界面上選擇“MTP On-board VDD limitation” 或 “On-board Program”

(請參考燒錄器 PDK5S-P-003 的用戶手冊)。