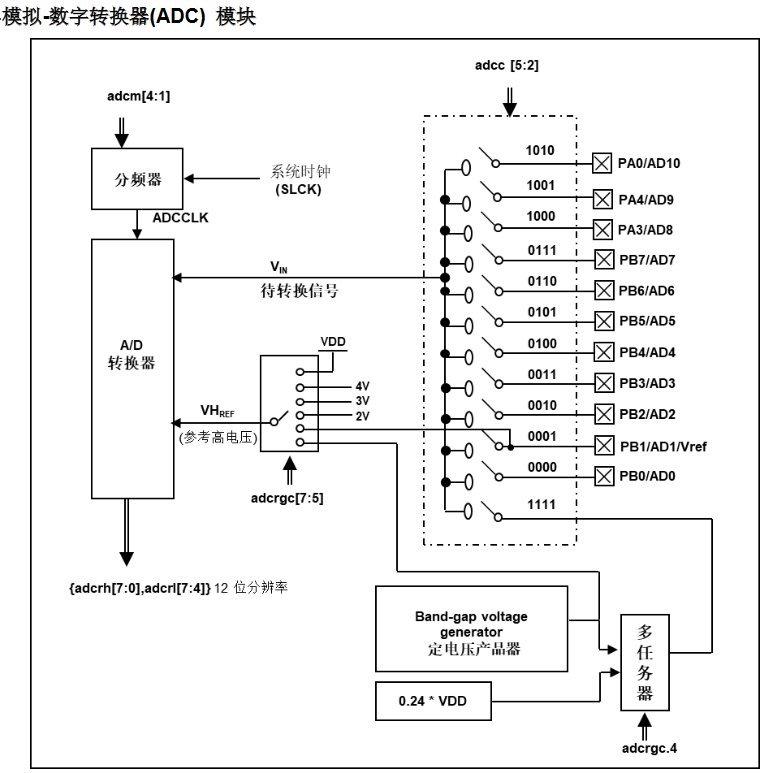

當使用 ADC 模塊時有 7 個寄存器需要配置,它們是:

ADC 控制寄存器(adcc)

ADC 調節控制寄存器(adcrgc)

ADC 模式寄存器(adcm)

ADC 數據高位/低位寄存器(adcrh, adcrl)

端口 A/B 數字輸入啟用寄存器(padier, pbdier)

如下是 ADC 裝進程的步驟:

(1) 通過寄存器 adcrgc 配置參考高電壓

(2) 通過 adcm 寄存器配置 AD 轉換時鐘信號

(3) 通過 padier

、pbdier 寄存器配置模擬輸入引腳

(4) 通過 adcc 寄存器選擇 ADC 輸入通道

(5) 通過 adcc 寄存器啟用 ADC 模塊

(6) 啟用 ADC 模塊之后,延遲一段時間

條件 1:使用 bandgap 1.2V 或 2V/3V/4V 相關電路時,無論是將其用作內部參考高電壓還是作為 AD 輸入通

道,所需的延遲時間必須超過 1ms;如果 200 個 AD 時鐘已經超過 1ms,那么延遲時間只需要 200 個 AD 時

鐘即可。當啟用內部 BG/2v/3v/4v 為參考高電壓時,必須保證 IHRC 為開啟狀態。

條件 2:沒有使用任何 bandgap 1.2V 或 2V/3V/4V 相關電路,延遲時間僅需 200 個 AD 時鐘。

另注意:以上兩條件所涉及的 200 個 AD 時鐘,該時鐘是指由 ADCM 寄存器配置后的 ADC 轉換時鐘而非系

統時鐘 SYSCLK。

(7) 執行 AD 轉換并檢查 ADC 轉換數據是否已經完成 adcc.6 設置 1 開啟 AD 轉換并且檢測 adcc.6 是否是‘1’。

(8) 從 ADC 寄存器讀取轉換結果:

先讀取 adcrh 寄存器的值然后再讀取 adcrl 寄存器的值。

應用時,如果是關掉 ADC 模塊后再重新啟用 ADC 的情況下,或者在切換 ADC 參考電壓及輸入通道時,進

行 ADC 轉換之前請重新執行如上步驟 6,確保 ADC 模塊已經準備好。

AD 轉換的輸入要求

PMS132/PMS132B

8 位 OTP 型單片機帶 12 位 ADC

© Copyright 2024, PADAUK Technology Co. Ltd Page 60 of 99 PDK-DS-PMS132(B)_CN_V108-Aug. 2, 2024

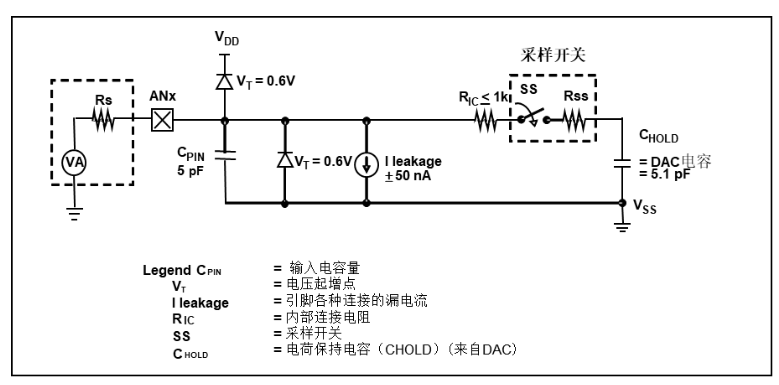

5.14.1 AD 轉換的輸入要求

為了滿足 AD 轉換的精度要求,電容的保持電荷(CHOLD)必須完全充電到參考高電壓的水平和放電到參考

低電壓的水平。模擬輸入電路模型如圖 21 所示,信號驅動源阻抗(Rs)和內部采樣開關阻抗(Rss)會直接影響到

電容 CHOLD 充電所需求的時間。內部采樣開關的阻抗可能會因 ADC 充電電壓而產生變化;信號驅動源阻抗會

影響模擬輸入信號的精度。使用者必須確保在采樣前,被測信號的穩定,因此, 信號驅動源阻抗的最大值與被

測信號的頻率高度相關。建議,在輸入頻率為 500khz 下,模擬信號源的最大阻抗值不要超過 10KΩ。

模擬輸入模型

在使用 AD 轉換之前,必須確認所選的模擬輸入信號的采集時間應符合要求,ADCLK 的選擇必須滿足最短信

號采集時間。

選擇參考高電壓

ADC 參考高電壓能夠通過寄存器 adcrgc 的位[7:5]來選擇,并且它的選擇有 VDD,4V,3V,2V,bandgap

(1.20V)參考電壓或者來自 PB1 外部引腳。

ADC 時鐘選擇

ADC 模塊的時鐘(ADCLK)能夠通過 adcm 寄存器來選擇,ADCLK 從 CLK÷1 到 CLK÷128 一共有 8 個選

項可被選擇(CLK 是系統時鐘)。由于信號采集時間 TACQ ADCLK 的一個時鐘周期,所以 ADCLK 必須滿足

這要求,建議 ADC 時鐘周期是 2us